# 嵌入式异构多核的片上通信架构设计

王颖 陈红 陈振娇

中国电子科技集团第五十八研究所，江苏省无锡市，214000；

**摘要：**针对现有内嵌异构众核芯片通讯结构难以实现有效异质众核协同的难题，本文拟深入研究内嵌异构众核系统对内核通讯和存储层面的差异化要求，构建“主-辅”协同调控模式框架，提升核心协同能力和数据传输能力。仿真结果表明，与传统的“RISC+DSP”结构相比，这种结构模式的性能提高了约23%。

**关键词：**片上通信；多核；处理器；嵌入式系统

DOI: 10.69979/3041-0673.25.10.020

## 引言

由于芯片制造技术进入了深亚微米，现代计算机系统架构的研究也开始转向多核架构。各大半导体厂商如英特尔、IBM、AMD等均已推出多核处理器产品。众核架构在提升CPU效能和降低功耗等方面都具有重要意义<sup>[1]</sup>。

在嵌入式异构众核技术中，最具代表性的是TI公司的“RISC+DSP”架构——OMAP，ARM处理器通过邮箱信息（Mailbox Message）与DSP通讯<sup>[2]</sup>。这两个系统由一个流控模块互联，与该流控系统相连的还有DMA控制器，SDRAM，FLASH等存储器件。OMAP中的片上通讯结构通过单独邮箱+单独DMA方式来实现，可以在一定程度上缓解DSP芯片对海量数据的需求，但是由于在芯片

中必须设置邮箱和DMA，从而消耗了芯片的带宽<sup>[3]</sup>。

为此，本文拟构建“主-辅”协同模式，其控制模式以信息控制单元为中心，包括增强型邮箱和简化DMA两大部分，并将两者有机结合起来，实现主、辅核间的通讯，以及辅核中的局部存储器与内存的交互。

## 1 计算密集型嵌入式异构多核处理器

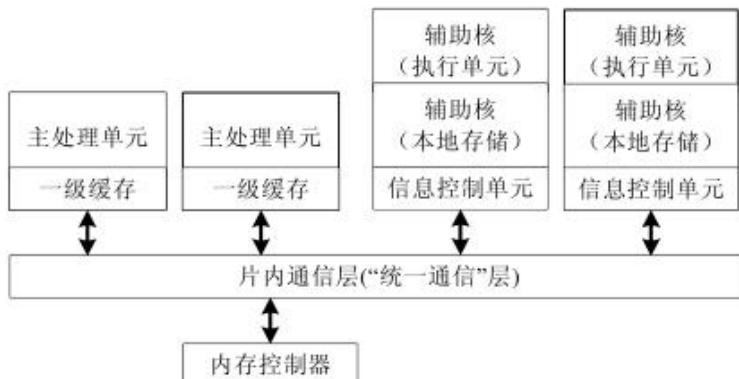

本文以嵌入式系统为背景，以支持SIMD进程的异质众核系统处理器为研究对象，开展数据匹配、检索、筛选等大规模数据处理。此处理器由主核与辅核组成，其中，主核负责系统的运行、应用软件的管理以及一般的计算等；辅核负责数据的比对和匹配等大量的运算<sup>[4]</sup>。具体架构见图1。

图1 嵌入式异构多核处理器原型架构图

由于辅核是以海量数据为主体的计算密集型处理器，其主要用途是模式识别、噪声辨识等，因此对其设计提出了更高的要求。从图1中可以看到，辅核由执行单元、本地存储和信息控制单元三部分组成。执行单元完成特定的数据处理工作，其执行命令及数据均来自于本地存储器。信息控制器负责辅核与外部设备的通信，以及局部存储器与其他设备的海量数据交互。

主核执行时，可以访问整个系统的空间，辅核读取和储存的数据仅在局部存储器中进行。在此基础上，将主核与辅核通过分层的方式进行互连。同时，因为该架构是针对计算密集型的应用需要，所以为了加快数据的储存速度，在片内通讯层级上也加入了一个存储单元控制器。

## 2 “主-辅”通信架构模型设计

主核具有对整个系统的管理功能，在操作系统的背景下，通过主核向辅核派发计算密集型的处理任务，并将数据从系统地址空间向局部地址空间转移。由于运算密集的任务通常具有海量的数据传输，因此，若任务中大部分工作都是主核访问辅核的局部存储器，并从局部存储器传输到主核的本地存储器，那么该进程必然会对主核的运算资源造成巨大的消耗。同时，由于主核也要执行操作系统和其他非运算密集的程序，必然会严重制约整个系统的性能。此外，在具有多个辅核的架构中，主核必然要对每一个辅核派发大量的任务，从而导致整个系统的运行效率下降<sup>[5]</sup>。

为了解决这个问题，本文从芯片内部通讯的原理出发，进行通信架构模型设计。芯片内的通讯由两个环节组成：一是运算密集度高的工作，所有的计算密集的任务都被加载到主核内部，这部分的通讯本质上就是在主核的内部存储器与辅核的局部存储器间的海量数据的传输，即数据搬运类的通信；第二个环节是在执行期间，辅核与主核进行通讯并同步。

在进行处理器通讯模式的设计时，需要将这两种通讯方式分开来进行。这是由于两种类型的通讯在不同频率、不同数据大小的情况下，若按同样的方法进行处理，会使芯片的性能在一定程度上受到影响。

在此基础上，提出了基于“主-辅”模式的嵌入式异质众核系统通讯体系结构。其主要思路是由主核负责派发任务给辅核，辅核负责运行相关命令。这个体系结构需要辅核自行完成任务的提取和运行，从而成为辅核的性能瓶颈。辅核的指令系统、执行体系结构以及所采用的函数并不适合执行这样的内存密集型运算。所以，基于这个思路，我们建立了一个独立的、主-辅核之间连接的信息处理模块，实现了各子系统间的信息处理和辅助处理。

此外，本文还研究主核与辅核间的信息通讯以及数据同步问题，此类信息传输所需的信息数量非常少，通常由多个核心发送。为了满足这种要求，本文提出把邮箱的模式拓展到信息控制单元上，使其能够实现主、辅核间的少量数据通讯。即在信息控制单元中设立若干邮箱，主核与辅核之间通过邮箱发送和接收信息来实现通讯。

因此，我们对此邮箱结构进行了扩展，使其与系统相适应。设定若干以信息控制单元为导向的邮箱，主核可以将少量的数据量信息以报文形式传送到邮箱中，同

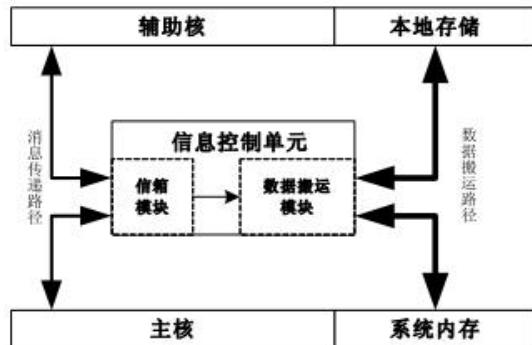

时，邮箱的信息在信息控制单元的数据处理模块进行处理。鉴于辅核还可以启动数据处理，因此，本文对辅核进行了适当的适配。通过扩展，无需在数据处理类型的通讯中配置信息接收器。通讯模式的基本体系结构如图2所示。

图2 “主-辅”控制模型主要架构图

从图2可以看出，信息控制单元主要由邮箱模块与数据搬运模块组成。邮箱模块是报文传输通道的转接部分，主要用于主核与辅核间的通讯信息的传输。同时，也存储从主核与辅核传送来的数据，并将信息传输到数据搬运模块，实现在局部存储器与存储器间的数据传输。

总体来说，在主、辅核间建立了一套专门的信息控制单元，该控制单元中的扩展邮箱模块和数据搬运模块协同工作，使主、辅核间的两种通讯方式均能很好地实现。另外，因为信息控制单元是与主、辅核分离的，所以主、辅核可以在执行其它工作的情况下，完成海量数据的通讯，从而极大提升了整个系统的总体性能。

在具体实施过程中，我们把信息控制单元与辅核结合起来，形成一个副处理器子系统。因为辅核无法与其它部件直接通讯，只能通过信息控制单元来完成，所以无法与芯片内部的互联总线相连，其次，信息控制单元的主要作用就是实现在系统内存与辅核本地存储间的数据传输，因此必须具备对系统内存与局部存储的直接存取能力。这不仅对通讯控制系统的设计提出了更高的要求，同时也对系统中的数据进行了处理。

### 3 通信过程

#### 3.1 主核向辅核发起通信的基本程序如下所示：

- 1) 主核向邮箱模块传输通讯信息；

- 2) 邮箱模块对信息进行接收和储存；

- 3) 辅核经由信息控制单元的邮箱模块取得信息。

在此要明确指出，辅核并不清楚什么时候主核将发出信息。因此，在当前的通讯流程中，第3阶段辅核应

该采取轮询的方法，持续地对邮箱模块进行访问，同时获取所需的信息。与轮询相应的是中断模式，但是因为这各辅核的类型比较特殊，所以在执行大量运算时，数据量非常庞大，不适用于转换成本过高的情况下提供中断服务。

### 3.2 辅核向主核发起通信的基本程序如下所示：

- 1) 辅核向信息控制单元的邮箱模块传输通讯信息；

- 2) 邮箱模块在将中断信号发送给主核时，接收和储存信息；

- 3) 主核接收到中断信号后，从信息控制单元的邮箱模块取得通讯信息。

这种通信处理与主核向从何发起通信之间最大的区别在于，当辅核分配到主核的信息被邮箱模块收到时，邮箱模块会发出一个中断信号。在此基础上，主核能够实时地获得通讯信息。这是因为主核是整个系统的核心，所以具有独立的中断功能。采用中断技术实现了对主机进行数据采集，无需对主机进行轮询，这样就减少了在执行期间的资源浪费，可以为其它任务提供更多的资源。

### 3.3 主核发起数据搬运类通信的基本流程如下所示：

- 1) 主核向信息控制单元的邮箱模块发送信息；

- 2) 邮箱模块对控制信息进行接收和储存；

- 3) 数据搬运模块从邮箱模块取得信息，并执行信息传输任务；

在此流程中，第3阶段的数据搬运模块对邮箱进行轮询，以便及时执行对应的任务。因为数据搬运模块是一个完全的硬件组件，仅承担着接收和执行的任务，所以使用轮询的方法来获得信息不会导致本身的操作效率下降。另外，由于数据搬运模块与邮箱模块都是信息控制单元的组件，因此两者通讯是通过一条内路径来实现的，无需经过片内通讯信道，所以在操作过程中也不会增大通信数量。

## 4 测试与分析

“主-辅”通讯模式以连接辅核的信息控制单元为核心，其核心部分为具有扩充功能的邮箱和低功耗DMA控制器。然而，目前主流的内嵌异构众核芯片中，通常使用OMAP等异质众核体系结构，其中，CPU通过单独邮箱与辅核DSP通讯，辅核通过单独的DMA控制器来实现本地cache和本地存储的交互。为此，本文对这两种方

法进行了对比，从而对这种通讯模式进行了性能分析。

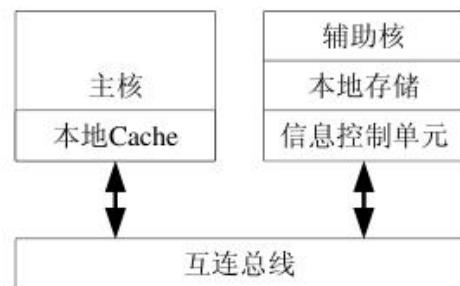

图3 应用“主-辅”模型的异构多核处理器原型图

以“主-辅”模式为基础的异质众核体系结构（为了便于描述，以下简称A体系结构）如图3所示，该体系结构包括主核与本地cache、辅核与本地存储及信息控制单元，两个处理器之间由内部互联总线相连。

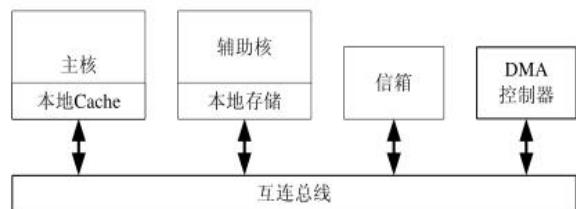

而在图4中显示了一种异质众核（以下简称B体系结构），该体系结构使用了行业中普遍使用的典型模式，包括主核与本地cache、辅核与本地存储、单独的邮箱和单独的DMA控制器，邮箱组件的容量与A中的消息控制单元相同，两个核都通过互联总线与其他模块相连。

图4 应用经典通信模型的异构多核处理器原型图

对于A和B两种架构，本文做了一个仿真器的仿真实验。在具体实施过程中，所有主核均为32 bits的MIPS I指令集，使用传统的五级流水，并且包括两通道8 KB的L1P Cache和四通道8 KB的L1D Cache，辅核使用改进后的32 bits MIPS I，使用传统五级流水，具有16 KB局部存储空间。两种体系结构的总线均使用32 bits的无水流的总线来实施。所有核的频率相同，并且都是总线频率的4倍。

分别用A和B两种仿真软件对该软件进行了测试，得到了如下的测试结果：

表1 通信架构模型测试结果

| 类型   | 主核  | 辅核  | 总计  |

|------|-----|-----|-----|

| A 架构 | 259 | 424 | 683 |

| B 架构 | 245 | 592 | 837 |

在A架构完成整个测试过程所需的通讯成本为683，主核消耗259个总线周期，辅核消耗424个总线周期；而B架构完成整个测试过程所需的通讯成本为837，主

核消耗 245 个总线周期，辅核消耗 592 个总线周期，由于在本次试验期间 DMA 仅用于辅核，因此 DMA 控制器占据了辅核的总线周期。

从表 1 可以看出，A 体系结构所需要的通信总量仅为 B 体系结构的 81.6%，因此，“主-辅”体系结构的整体效能应该是 B 体系结构体系结构的 1.23 倍。

通过对 B 体系结构的分析，我们还可以看到，B 体系结构下的主核的通讯开销有所降低，这是因为 B 体系结构中 Mail 与 DMA 两个控制器各自独立的结构，避免了碰撞，因此缩短了总线通讯时间。但是，在 B 体系结构中，辅核的开销要比 A 体系结构中高得多。这有两个方面的原因：第一，在 B 体系结构中，因为邮箱与辅核是分离的，所以辅核必须频繁地轮询邮箱，这样会导致系统的开销增大。其次，因为 DMA 控制器也是离散的，所以辅核和主核都必须经由总线来进行数据传输，这样就会造成总线通讯成本的提高。

综上，本文提出的通讯模式相比于传统的嵌入式异质众核处理器通讯模式具有一定的优越性。

## 5 总结

针对现有内嵌异构众核芯片通讯结构难以实现有效异质众核协同的难题，本文提出了一种基于“主-辅”模式的多核系统，并对其在芯片上的通讯体系结构进行了深入的研究和分析。本文以“主-辅”模式为基础，研究适用于嵌入式异质众核机的新型芯片通讯模式，并

利用硬件平台与仿真器对所提方案进行实验与分析。

通过仿真实验，证明了与传统的异质众核体系结构相比，本文提出的体系结构模型具有更好的性能。

## 参考文献

- [1] 范文杰,周牧也,朱凌晓,李世平,陈铠,邓松峰,何国强,冯书谊,宋文清,李丽,傅玉祥.用于 MIMO 检测的基于 NoC 的多核动态可重构架构 [J].现代电子技术,2024,47(21):1-6.

- [2] 冀峰.基于 OMAP 架构的无线终端双核通信设计及优化 [J].计算机与网络,2022,48(01):56-59.

- [3] 李智慧,张双,刘帜琦,万欣宇.PowerPC 多核处理模块性能测试方法研究 [J].长江信息通信,2023,36(04):121-123.

- [4] 刘刚.基于 LCM 的分布式嵌入式消息通信中间件设计 [J].工业控制计算机,2024,37(08):13-15+18.

- [5] 董旭斌,何世彪,李成勇,陆鹏.嵌入式网络通信远程数据传输功耗准确预测 [J].计算机仿真,2024,41(1):545-549.

作者简介：王颖（1991-），男，汉族，江苏省无锡市，硕士研究生，职位：IC 设计师，职称：工程师，研究方向：芯片设计，单位：中国电子科技集团公司第五十八研究所。