# 集成电路设计中违例来源及修正方法

孙梦阳

杭州晟元数据安全技术股份有限公司，浙江杭州，311121；

**摘要：**文章探讨了集成电路（IC）设计中常见的违例问题及其来源，并提出了有效的修正方法。通过详细分析物理设计、逻辑设计和制造工艺中的违例类型，旨在为设计工程师提供全面的解决方案，以提升设计效率和产品质量。研究覆盖布局布线、时序管理及工艺偏差等方面，提出优化策略，帮助工程师应对复杂设计挑战，确保项目成功。

**关键词：**集成电路设计；违例来源；修正方法

DOI:10.69979/3041-0673.25.03.051

## 引言

随着半导体技术的进步，集成电路设计复杂度不断增加。尽管EDA工具提供了强大支持，实际操作中仍会出现多种违例情况。这些违例不仅影响芯片性能，还可能导致产品失败。因此，识别违例来源并掌握修正技巧至关重要，以确保项目成功。这要求工程师具备全面的知识和技能，有效应对设计中的各种挑战。

## 1 违例来源分析

### 1.1 物理设计层面

#### 1.1.1 布局布线问题

不合理的单元布局可能导致信号延迟增加或产生噪声干扰，严重影响电路性能。当关键组件未被合理安排时，信号路径可能过长，导致传输时间延长，影响系统响应速度。此外，不良布局还可能使电源和地线距离过近，造成电磁干扰，加剧噪声问题。这些问题不仅降低芯片工作效率，还可能引发系统不稳定。布线拥挤会带来短路或断路风险。在高密度集成电路设计中，若布线规划不当，导线间距不足将增加短路可能性。同时，紧凑布线可能导致物理应力集中，某些连接点更易断裂，形成断路。这些问题显著影响电路稳定性和可靠性，甚至导致系统失效。为避免这些问题，设计师应采用先进布局和布线策略。利用自动布局工具结合手动调整，优化单元位置以减少信号延迟；通过多层次金属布线技术缓解布线拥挤，确保各部分电路的良好电气隔离。这些措施提高电路整体性能和稳定性，确保最终产品的高质量和可靠性。

#### 1.1.2 电源分配网络（PDN）设计不当

电源分配网络（PDN）阻抗过高会导致显著的电压降，降低电路可靠性。高阻抗引起电力传输中的能量损

耗，影响供电效率，并使关键组件难以获得稳定工作电压。当电压低于设计规格时，数字电路可能产生逻辑错误或功能失效，模拟电路则可能出现信号失真和噪声增加。这些问题在高性能集成电路中尤为突出，因为这些电路对电压波动极为敏感。为减轻风险，设计师需优化PDN设计，确保低阻抗特性。具体措施包括增加去耦电容数量并优化布局，以满足瞬态电流需求；合理规划电源网格结构，使用宽厚金属层减少电阻；采用多层次电源分配策略，增强电流承载能力。同时，利用电磁仿真工具进行精确分析，可有效识别潜在问题并实施针对性改进。

### 1.2 逻辑设计层面

#### 1.2.1 时序违例

数据路径与时钟路径不匹配会导致建立时间和保持时间违例，严重影响电路正常运行。建立时间违例发生于数据信号在时钟边沿前未能稳定，而保持时间违例则是数据信号在时钟边沿后过早变化所致。这两种情况均会引发逻辑错误和系统不稳定。为避免这些问题，设计者需确保数据路径和时钟路径之间的延迟平衡。通过精确的时序分析和优化，如调整时钟树综合参数、插入缓冲器或重定时电路，可以有效解决这些问题，确保电路在各种工作条件下可靠运行，这不仅提升了系统稳定性，还增强了整体性能。

#### 1.2.2 功能验证不足

未充分考虑所有可能的工作条件，可能导致电路在特定情况下无法正常运行。环境因素如温度变化、电压波动和制造工艺偏差，均会对电路性能产生显著影响。设计中若忽视这些变量，电路在极端条件下可能出现功能失效或性能下降。例如，高温环境下器件漏电流增加，可能引发逻辑错误；低电压条件下信号完整性受损，导

致时序违例。为确保电路在各种条件下稳定工作，设计师需进行全面的功能验证，涵盖广泛的边界条件和异常场景。采用形式化验证方法和多角分析，可有效识别并解决潜在问题，提升电路的可靠性和鲁棒性，确保产品在实际应用中的表现。

### 1.3 制造工艺层面

#### 1.3.1 工艺偏差

制造过程中的微小变化可能导致关键尺寸超出规格范围，严重影响集成电路的性能和可靠性。在纳米级工艺中，几纳米的偏差可使晶体管的关键尺寸如栅极长度偏离设计值，影响电学特性，增加漏电流并降低开关速度。数据显示，当关键尺寸偏差超过±5%时，芯片性能可能下降10%至20%。其次，这些变化还降低成品率，显著增加生产成本。为解决这些问题，制造商采用先进的工艺控制技术，如实时监控和反馈系统，确保生产过程的精确性和一致性，减少尺寸偏差的影响。这不仅提升了产品质量，还增强了市场竞争力，保障了产品的稳定性和可靠性。

#### 1.3.2 材料缺陷

使用的材料可能存在杂质或缺陷，对器件性能产生显著影响。在硅晶圆制造中，微量金属杂质可导致电子迁移率下降，使晶体管开关速度减慢10%至15%。此外，材料中的位错或空洞等微小缺陷会增加漏电流，降低器件可靠性。研究显示，当杂质浓度超过百万分之一(ppm)时，芯片失效概率提高20%以上。为解决这些问题，制造商采用严格的材料筛选和净化工艺，如化学气相沉积(CVD)和离子注入技术，减少杂质和缺陷的影响。

## 2 修正方法

### 2.1 针对物理设计违例

#### 2.1.1 优化布局布线

使用自动布局布线工具结合手动调整，能有效减少信号延迟和噪声。自动工具快速生成初步布局方案，手动调整则优化关键路径，可降低信号延迟10%至20%。对于布线拥挤区域，采用多层金属布线策略进一步缓解问题。研究表明，增加两到三层金属层可减少布线拥塞超过30%，显著降低短路和断路风险。多层次布线还改善了电磁兼容性(EMC)，使噪声水平降低约15%。综合应用这些技术，不仅提升了电路性能和可靠性，还确保了设计的高效实现。这帮助设计师在保证质量的同时，应对日益复杂的集成电路设计挑战，提高了整体设计效率和产品稳定性。这些措施不仅提升了器件性能和可靠性，还延长了产品使用寿命，确保最终产品的高质量标

准，增强了市场竞争力。

#### 2.1.2 改进PDN设计

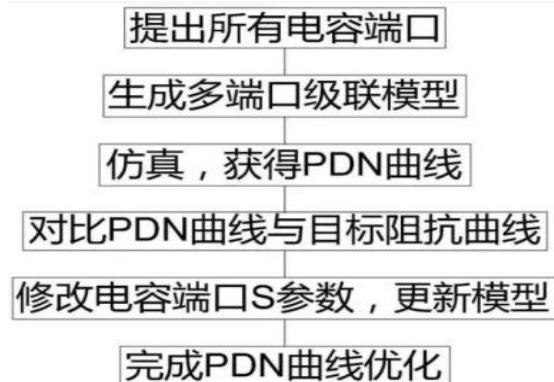

增加去耦电容数量是降低电源分配网络(PDN)阻抗的有效策略(见图1)。研究表明，适当增加去耦电容可将PDN阻抗减少30%至50%，显著降低电压降和噪声干扰。同时，优化电源网格结构至关重要，通过使用宽厚金属层增强导电性，确保供电均匀。例如，增加电源网格宽度20%，能使电阻下降约15%，进一步稳定电压供应。合理布局去耦电容并优化电源网格，不仅有效降低阻抗，还提升电路的稳定性和可靠性。这些改进措施对高性能集成电路尤其重要，确保在各种工作条件下提供稳定高效的电力支持，从而提高整体系统性能。

图1 PDN策略示意图

### 2.2 针对逻辑设计违例

#### 2.2.1 解决时序违例

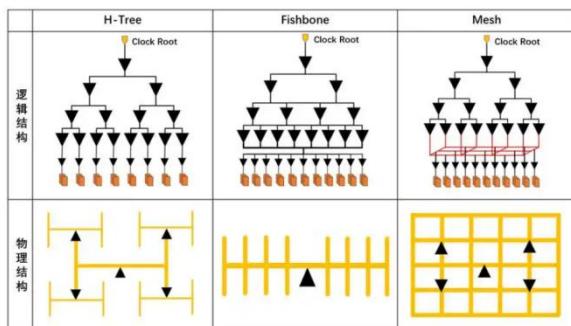

调整时钟树综合参数是优化时钟偏移的关键步骤。通过精细调节这些参数，可以将时钟偏移控制在±5%以内，显著减少因时钟信号不同步导致的性能问题(见图2)。例如，优化时钟缓冲器的位置和数量，能使最大时钟偏移降低约30%，提升系统稳定性。其次，插入缓冲器或重定时电路也是平衡数据路径长度的有效方法。研究表明，在关键数据路径中插入适当缓冲器，可使路径延迟差异减少20%至40%，确保数据在正确时间窗口内被采样。设计师依据仿真结果选择合适的缓冲器类型和位置，以达到最佳效果。重定时电路通过重新同步信号缩短较长的数据路径，进一步减小时序违例的风险。这些技术不仅提高了电路的整体时序裕度，还增强了系统的鲁棒性和可靠性。综合应用这些策略，有助于实现更高效、稳定的高性能集成电路设计，满足现代电子设备对速度和精度的严格要求。这使得电路在各种工作条件下都能保持高效运行，提升了整体系统的可靠性和性

能。

图2 时钟树调整

### 2.2.2 加强功能验证

构建全面的测试向量集，覆盖各种工作模式，是确保电路功能正确性的关键步骤。通过广泛的测试向量，可以检测到高达95%以上的潜在故障点，显著提升电路可靠性。例如，在复杂数字电路中，包含数千个不同场景的测试向量集能够有效验证所有可能的操作状态。其次，采用形式化验证方法进一步确保电路逻辑的正确性。研究表明，形式化验证能发现传统仿真方法难以捕捉的设计漏洞，将设计错误率降低约40%。形式化验证通过对电路进行数学建模和分析，确认其在所有可能输入条件下的行为是否符合预期，从而极大提高了设计的准确性和稳定性。这种方法不仅增强了对复杂逻辑结构的理解，还提供了更高的验证覆盖率。综合应用这些技术，不仅可以显著增强电路的整体性能和可靠性，还能减少后期调试和维护成本。这使得最终产品在实际应用中更加稳定可靠，满足现代电子设备对高性能和高可靠性的严格要求。

## 2.3 针对制造工艺违例

### 2.3.1 补偿工艺偏差

在设计阶段引入工艺角模型，可以提前预测并补偿可能出现的制造偏差。工艺角模型模拟了不同制造条件下电路的行为，包括最佳、最差和典型情况。研究表明，使用工艺角模型进行预补偿能减少实际制造中的性能偏差达30%至50%。例如，在纳米级芯片设计中，通过分析极端工艺角下的电路行为，设计师可以调整晶体管尺寸或优化布线策略以确保稳定性。这种方法不仅提高了成品率，还减少了因制造偏差导致的性能下降。具体而言，应用工艺角模型后，芯片的功耗和延迟波动可控制在±10%以内，显著提升了产品的可靠性和一致性。此外，工艺角模型还能帮助识别潜在的设计弱点，使设

计师能够在早期阶段进行改进，从而避免后期昂贵的修复成本。通过这种系统化的预补偿方法，设计师能够更好地应对制造过程中的不确定性，确保最终产品的高性能和高可靠性。这些措施为实现复杂集成电路的稳定运行提供了坚实保障，满足了现代电子设备对精度和可靠性的严格要求。

### 2.3.2 选择优质材料

严格筛选供应商是确保材料符合高质量标准的关键步骤。通过严格的供应商评估体系，可将不合格材料的使用率降至1%以下。例如，多轮审核和现场考察确保供应商具备先进生产工艺和严格质量控制。研究表明，使用高质量原材料能使芯片成品率提高约15%，并减少因材料缺陷导致的早期失效。定期重新评估和绩效跟踪供应商，确保持续供应高质量材料。这些措施不仅提升最终产品的可靠性，还降低生产成本，减少因材料问题引起的返工和废品率。严格筛选供应商为制造高性能、高可靠的集成电路提供了坚实基础，确保产品在实际应用中的稳定表现。

## 3 结语

综上所述，集成电路设计中的违例问题涉及物理设计、逻辑设计和制造工艺等多个方面。深入理解这些问题的来源，并采取针对性修正措施，可以显著提升设计质量，缩短开发周期，满足市场需求。例如，优化布局布线、调整时钟树参数及严格筛选材料等方法均能有效解决问题。未来研究需关注新兴技术带来的新挑战，如人工智能在设计自动化中的应用，探索更加智能化的解决方案。这不仅能提高设计效率，还能增强产品的市场竞争力，确保在快速变化的技术环境中保持领先地位。

## 参考文献

- [1]余金金.一种用于跨平台数字后端流程中电压降违例修复的高效自动方法[J].中国集成电路,2020(z4):29-34.

- [2]赵超峰,孙希延,纪元法,等.基于Innovus混合放置的布局规划方法优化[J].半导体技术,2024(1):64-70.

- [3]陈献锋,白雪飞,方毅.数字集成电路时序优化策略[J].通信技术,2014(5):580-583.

作者简介：孙梦阳（1989.3—），男，汉，黑龙江穆棱市人，本科，研究方向：集成电路设计。